https://prism.ucalgary.ca

The Vault

Open Theses and Dissertations

2014-09-30

## Mixerless Transmitters for Wireless Communication

## Illath Veetil, Suhas

Illath Veetil, S. (2014). Mixerless Transmitters for Wireless Communications (Master's thesis, University of Calgary, Calgary, Canada). Retrieved from https://prism.ucalgary.ca. doi:10.11575/PRISM/26926 http://hdl.handle.net/11023/1887

Downloaded from PRISM Repository, University of Calgary

#### UNIVERSITY OF CALGARY

Mixerless Transmitters for Wireless Communications

by

Suhas Illath Veetil

#### A THESIS

# SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

GRADUATE PROGRAM IN ELECTRICAL AND COMPUTER ENGINEERING

CALGARY, ALBERTA

SEPTEMBER, 2014

© Suhas Illath Veetil 2014

#### **Abstract**

There is immense research in developing digital transmitters that are multi-standard and reconfigurable. A promising technique is RF Digital to Analog Converter (RFDAC), where the input digital baseband signal is directly converted to an analog RF signal. The existing RFDAC based transmitters use mixers and adopt filtering to avoid mixer spurs. Polar transmitters too use mixers and need filtering. The use of RF filtering in these transmitter topologies limits the bandwidth and therefore the multi-standard reconfigurability of such transmitters.

This thesis aims to develop mixerless transmitter architectures that are reconfigurable. A mixerless polar modulator-based transmitter and a mixerless three-way amplitude modulation based transmitter are proposed for OFDM signals. The proposed architectures translate the baseband signal to RF without using mixers. The topologies do not have any emissions over a wide frequency band. The large RF bandwidth and the absence of filters make the designs more reconfigurable and suitable for integration.

#### Acknowledgements

I take this opportunity to place on record my deep sense of gratitude to my supervisor, Dr. Mohamed Helaoui for his guidance, care, patience and illuminating discussions throughout my work. Without his supervision and constant help through constructive comments, this thesis would not have been possible.

I am grateful to my professor Dr. Fadhel M. Ghannouchi for providing me an excellent opportunity to do this work in his research group and providing the best facilities and atmosphere for the development of this thesis.

I thank my committee members Dr. Reda Alhajj and Dr. Kartikeya Murari for their valuable comments and advice on the thesis work.

Special thanks to Andrew Kwan and Mohammadhassan Akbarpour, PhD candidates and Dr. Mehdi Vejdani Amiri, Post-Doctoral Fellow for helping me with their advice regarding experiments in the lab. I would like to thank Ivana D'Adamo, administrative support staff and Chris Simon, technical support staff for their help and support. I thank each and every member of the iRadio Labs for their support and friendship throughout my work.

I remember with gratitude, the cooperation and help given to me by my friends and also for finding time for the long Badminton games.

I thank my parents, sisters and brothers-in-law for their constant support and motivation throughout my life.

To my friends

## **Table of Contents**

| Abstract                                        | ii   |

|-------------------------------------------------|------|

| Acknowledgements                                | iii  |

| Dedication                                      | iv   |

| Table of Contents                               | v    |

| List of Tables                                  | ix   |

| List of Figures and Illustrations               | x    |

| List of Symbols, Abbreviations and Nomenclature | xiii |

| Chapter One: Introduction                       | 1    |

| 1.1 Radio transmitter fundamentals              | 4    |

| 1.2 Transmitter key parameters                  | 5    |

| 1.2.1 Linearity                                 | 5    |

| 1.2.2 Error vector magnitude                    | 6    |

| 1.2.3 Adjacent channel power ratio              | 7    |

| 1.3 Digital radio transmitters                  | 8    |

| 1.3.1 RFDAC fundamentals                        | 9    |

| 1.3.2 Suppression of RFDAC emissions            | 11   |

| 1.4 Polar transmitters                          | 15   |

| 1.4.1 Envelope and phase signal recombination   | 16   |

| 1.5 Vector modulators                           | 21   |

| 1.6 Summary of transmitter architectures        | 23   |

|   | 1.7 Goals and objectives                                             | 24 |

|---|----------------------------------------------------------------------|----|

|   | 1.8 Thesis outline                                                   | 26 |

|   | 1.9 Conclusion                                                       | 28 |

| C | hapter Two: Amplitude Modulation using Variable Gain Amplifier (VGA) | 29 |

|   | 2.1 Introduction                                                     | 29 |

|   | 2.2 VGA fundamentals                                                 | 29 |

|   | 2.3 VGA as amplitude modulator                                       | 31 |

|   | 2.4 VGA imperfections                                                | 33 |

|   | 2.5 VGA calibration                                                  | 34 |

|   | 2.5.1 Memory polynomial calibration                                  | 34 |

|   | 2.5.2 Least squares technique                                        | 36 |

|   | 2.5.3 Digital predistortion technique                                | 38 |

|   | 2.6 Implementation                                                   | 40 |

|   | 2.7 Measurement results                                              | 41 |

|   | 2.8 Conclusion                                                       | 44 |

| C | hapter Three: Phase Modulation using Analog Phase Shifter            | 45 |

|   | 3.1 Introduction                                                     | 45 |

|   | 3.2 Phase shifter fundamentals                                       | 46 |

|   | 3.3 Phase shifter as phase modulator                                 | 48 |

|   | 3.4 Phase mapping                                                    | 50 |

|   | 3.5 Phase conditioning                                               | 51 |

|   | 3.5.1 Phase conditioning techniques                                  | 54 |

|   | 3.6 Phase shifter imperfections                                      | 56 |

|    | 3.7 Phase shifter calibration                                              | 57 |

|----|----------------------------------------------------------------------------|----|

|    | 3.7.1 Memory polynomial calibration                                        | 58 |

|    | 3.7.2 Digital predistortion of phase signal                                | 58 |

|    | 3.8 Phase modulator implementation                                         | 59 |

|    | 3.9 Measurement results                                                    | 60 |

|    | 3.10 Conclusion                                                            | 64 |

| Cl | napter Four: Mixerless Polar Modulator-Based Transmitter Architecture      | 65 |

|    | 4.1 Introduction                                                           | 65 |

|    | 4.2 Mixerless polar modulator-based transmitter                            | 65 |

|    | 4.3 VGA gain and phase response                                            | 66 |

|    | 4.4 Phase shifter gain and phase response                                  | 68 |

|    | 4.5 Calibration of the proposed transmitter architecture                   | 69 |

|    | 4.5.1 Modified memory polynomial calibration                               | 70 |

|    | 4.5.2 Digital predistortion technique                                      | 72 |

|    | 4.6 Transmitter implementation                                             | 73 |

|    | 4.7 Measurement results                                                    | 74 |

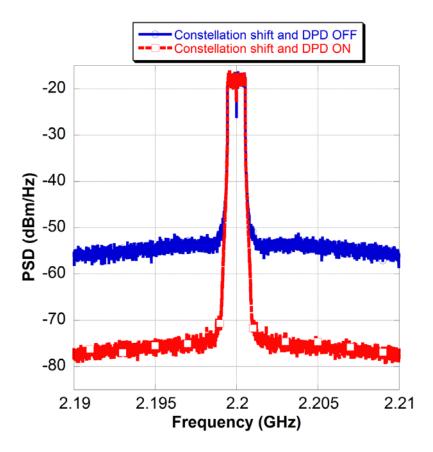

|    | 4.8 Constellation shift compensation                                       | 81 |

|    | 4.9 Conclusion                                                             | 85 |

| C] | napter Five: Three-way Amplitude Modulation-Based Transmitter Architecture | 86 |

|    | 5.1 Introduction                                                           | 86 |

|    | 5.2 Three-coordinate decomposition                                         | 87 |

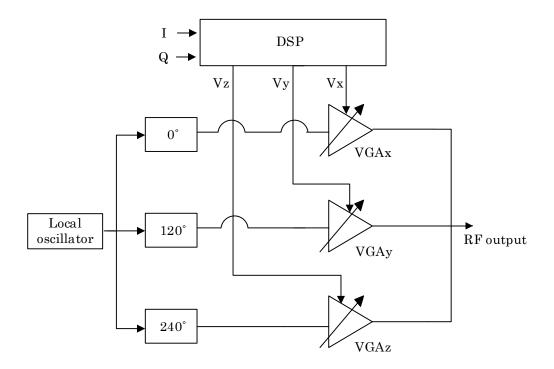

|    | 5.3 Three-way amplitude modulation-based transmitter architecture          | 89 |

|    | 5.4 VGA phase response                                                     | 90 |

| 5.5 Signal decomposition with phase error      | 91  |

|------------------------------------------------|-----|

| 5.6 VGA calibration                            | 92  |

| 5.6.1 Memory polynomial calibration            | 93  |

| 5.6.2 Digital predistortion technique          | 95  |

| 5.7 DSP block                                  | 96  |

| 5.8 Implementation of transmitter architecture | 99  |

| 5.9 Measurement results                        | 100 |

| 5.10 Conclusion                                | 105 |

| Chapter Six: Conclusion and Future Work        | 106 |

| 6.1 Summary of contributions                   | 108 |

| 6.2 Future work                                | 109 |

| References                                     | 111 |

## **List of Tables**

| Table 1.1 Summary of architectures                                                 | 23  |

|------------------------------------------------------------------------------------|-----|

| Table 1.2 Summary of phase modulation architectures                                | 23  |

| Table 2.1 Specifications of VGA ADL5330                                            | 33  |

| Table 2.2 Summary of performance of the VGA for LTE signal                         | 41  |

| Table 3.1 Specifications of phase shifter HMC928LP5E                               | 49  |

| Table 3.2 Summary of performance evaluation of phase shifter for LTE signal        | 60  |

| Table 4.1 Summary of performance evaluation of proposed transmitter for LTE signal | 74  |

| Table 4.2 Measured ACLR values of the proposed transmitter for LTE signal          | 75  |

| Table 4.3 Transmit EVM* specifications for wide area BS [85]                       | 75  |

| Table 4.4 ACLR requirements of E-UTRA (LTE) [85]                                   | 75  |

| Table 4.5 EVM measurements for LTE signal with 64 QAM constellations               | 77  |

| Table 4.6 Performance evaluation using LTE signals of 5 and 10 MHz bandwidth       | 78  |

| Table 4.7 Summary of performance evaluation of multi-branch topology               | 83  |

| Table 5.1 Summary of performance evaluation of proposed transmitter for LTE signal | 101 |

| Table 5.2 Summary of performance of direct conversion transmitters                 | 101 |

| Table 5.3 Performance evaluation of signal generator for LTE signal                | 102 |

## **List of Figures and Illustrations**

| Figure 1.1. Ideal software defined radio: (a) transmitter, (b) receiver          | 2  |

|----------------------------------------------------------------------------------|----|

| Figure 1.2. Conventional analog transmitter                                      | 3  |

| Figure 1.3. Conventional analog quadrature RF transmitter                        | 4  |

| Figure 1.4. Intermodulation: two-tone representation.                            | 5  |

| Figure 1.5. EVM measurement in constellation.                                    | 6  |

| Figure 1.6. RFDAC representation.                                                | 9  |

| Figure 1.7. Conventional transmitter with components replaceable with RFDAC [16] | 9  |

| Figure 1.8. Unit element of RFDAC proposed in [16].                              | 10 |

| Figure 1.9. RFDAC based direct-digital modulator proposed in [22].               | 13 |

| Figure 1.10. Conventional polar transmitter.                                     | 15 |

| Figure 1.11. Polar transmitter using DPAs.                                       | 17 |

| Figure 1.12. Polar transmitter architecture proposed in [37]                     | 18 |

| Figure 1.13. Block schematic of vector modulator                                 | 21 |

| Figure 1.14. Block schematic of proposed architecture                            | 24 |

| Figure 2.1. Block schematic of translinear VGA                                   | 30 |

| Figure 2.2. Block schematic of exponential type VGA.                             | 31 |

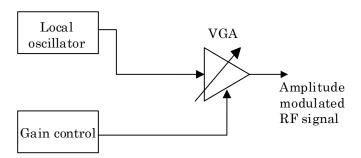

| Figure 2.3. VGA as an amplitude modulator.                                       | 32 |

| Figure 2.4. VGA gain and phase response.                                         | 33 |

| Figure 2.5. VGA forward gain model.                                              | 38 |

| Figure 2.6. VGA reverse gain model.                                              | 39 |

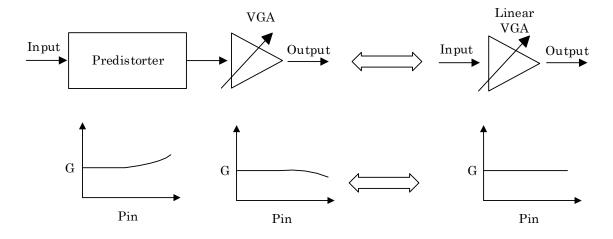

| Figure 2.7. Predistortion and linearization.                                     | 39 |

| Figure 2.8. Implementation of amplitude modulator using VGA                      | 40 |

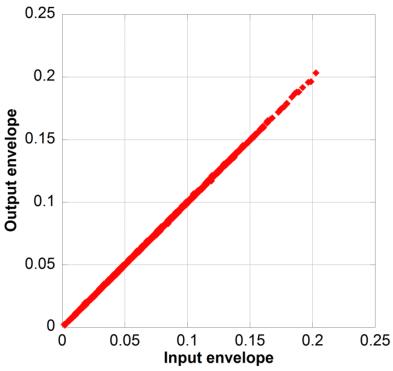

| Figure 2.9. Input-output envelope response of the VGA                            | 42 |

| Figure 2.10. Time domain envelope response of the VGA.                           | 42 |

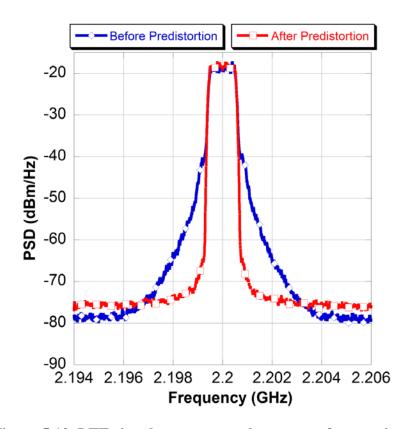

| Figure 2.11. VGA spectral response.                                                       | 43 |

|-------------------------------------------------------------------------------------------|----|

| Figure 3.1. DC equivalent circuit of analog phase shifter.                                | 47 |

| Figure 3.2. Phase modulator using phase shifter.                                          | 48 |

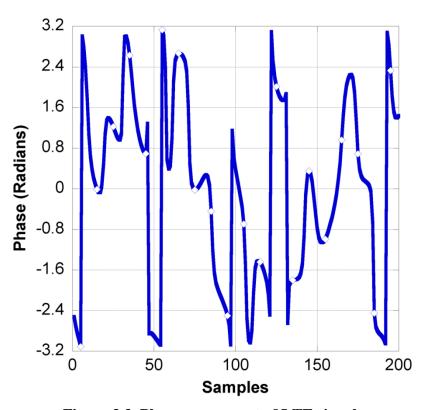

| Figure 3.3. Phase component of LTE signal.                                                | 50 |

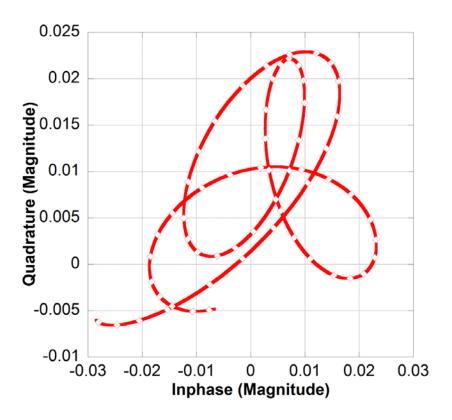

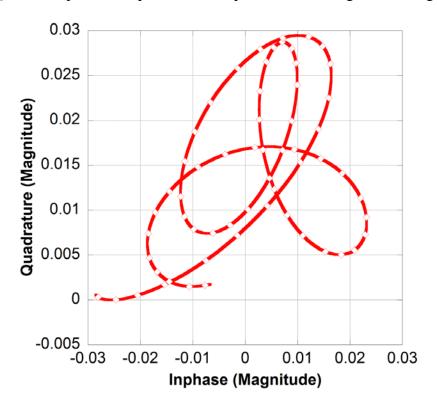

| Figure 3.4. LTE complex signal trajectory.                                                | 51 |

| Figure 3.5. DAC ringing effects on the phase voltage.                                     | 53 |

| Figure 3.6. LTE complex signal trajectory after constellation shift.                      | 55 |

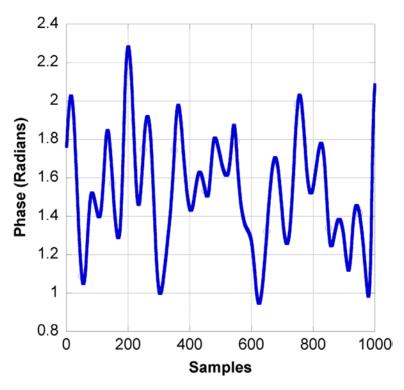

| Figure 3.7. Phase component of LTE signal after constellation shift.                      | 56 |

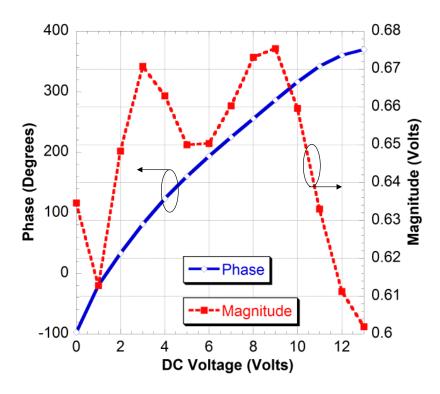

| Figure 3.8. Phase shifter dc gain and phase response.                                     | 57 |

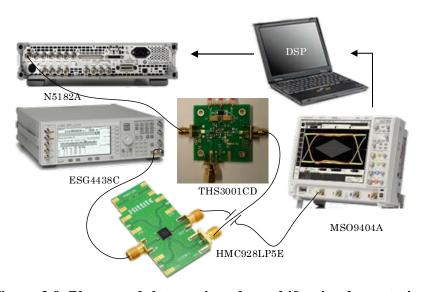

| Figure 3.9. Phase modulator using phase shifter implementation.                           | 59 |

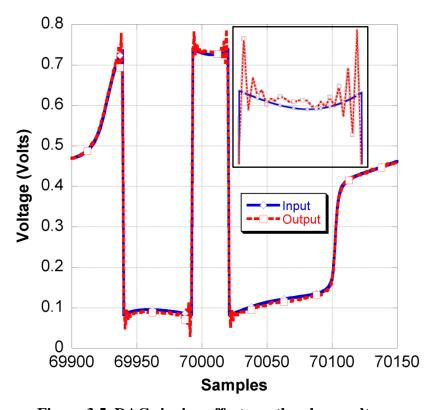

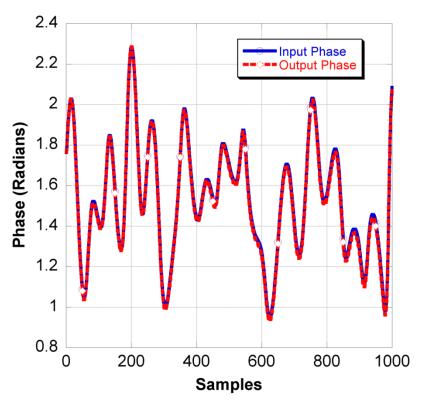

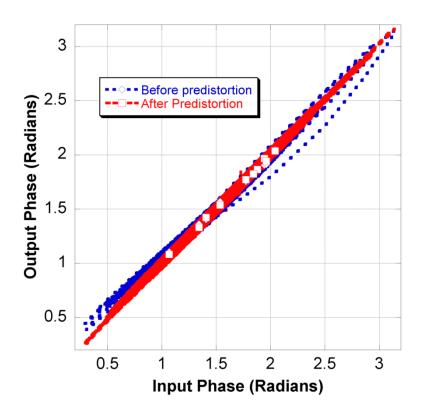

| Figure 3.10. Phase signal $(\Phi)$ at input and output of the phase shifter               | 61 |

| Figure 3.11. LTE signal spectrum at output of the phase shifter                           | 62 |

| Figure 3.12. Phase shifter input-output phase response                                    | 63 |

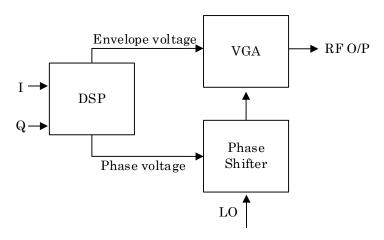

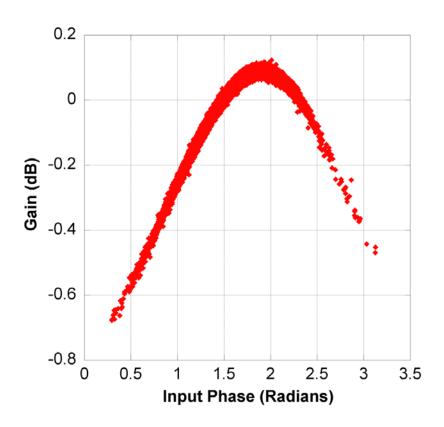

| Figure 4.1. Block diagram of the mixerless polar modulator-based transmitter architecture | 65 |

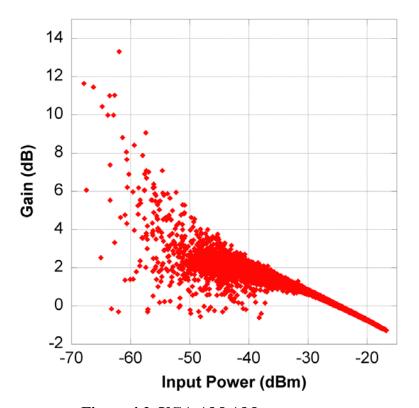

| Figure 4.2. VGA AM-AM response.                                                           | 66 |

| Figure 4.3. VGA AM-PM response.                                                           | 67 |

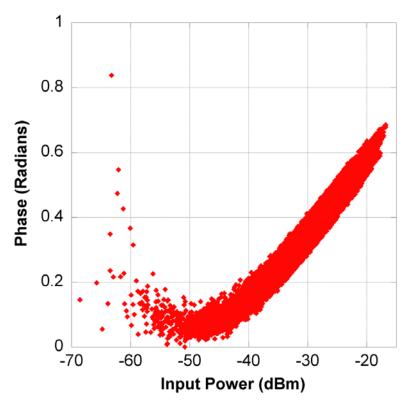

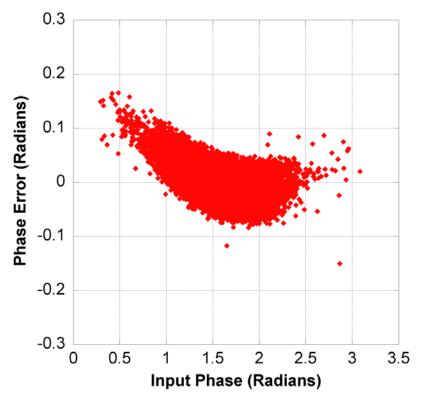

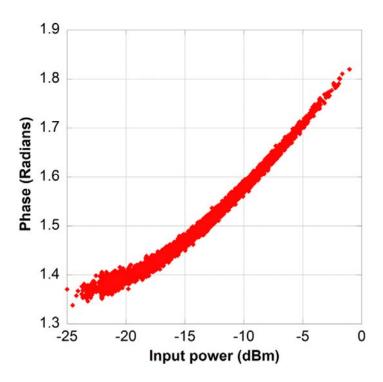

| Figure 4.4. Phase shifter PM-PM response                                                  | 68 |

| Figure 4.5. Phase shifter PM-AM response.                                                 | 69 |

| Figure 4.6. Block schematic of the proposed mixerless polar-modulator-based transmitter   | 72 |

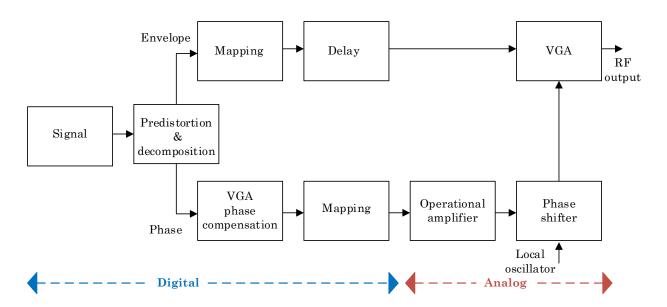

| Figure 4.7. Proposed transmitter architecture implementation.                             | 73 |

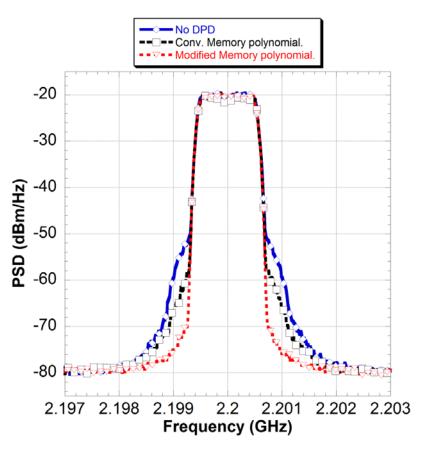

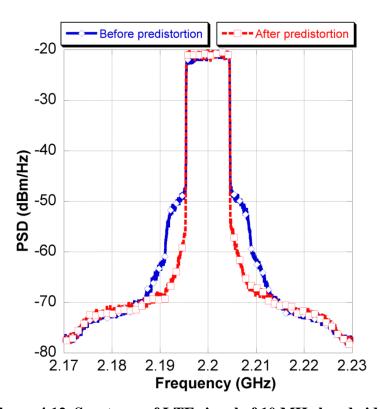

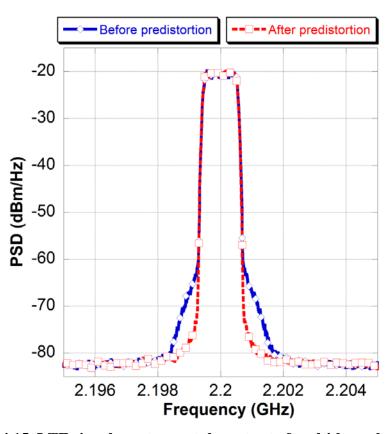

| Figure 4.8. LTE signal spectrum at the output of the polar transmitter                    | 76 |

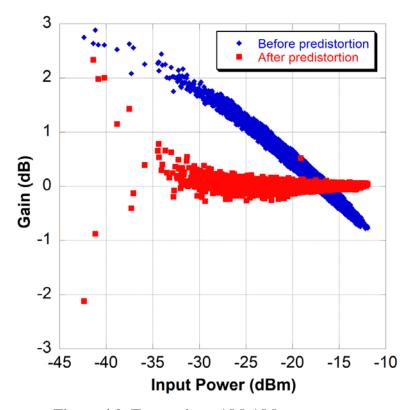

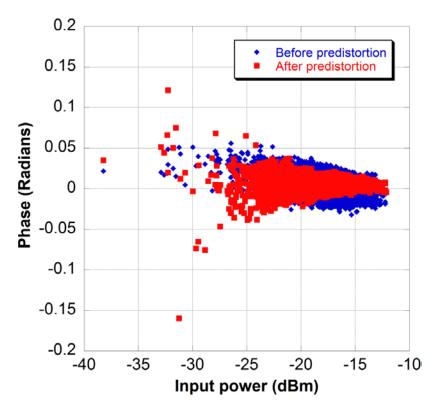

| Figure 4.9. Transmitter AM-AM response.                                                   | 77 |

| Figure 4.10. Transmitter AM-PM response.                                                  | 78 |

| Figure 4.11. Spectrum of LTE signal of 5 MHz bandwidth                                    | 79 |

| Figure 4.12. Spectrum of LTE signal of 10 MHz bandwidth.                                  | 79 |

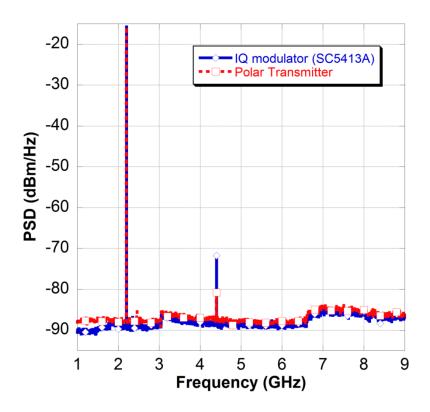

| Figure 4.13. Wide band spectral response of the proposed transmitter            | 80  |

|---------------------------------------------------------------------------------|-----|

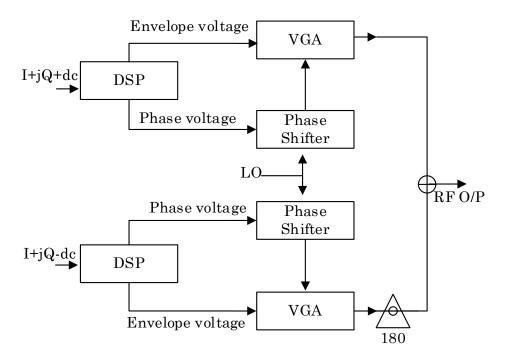

| Figure 4.14. Multi-branch polar modulator-based transmitter for dc compensation | 82  |

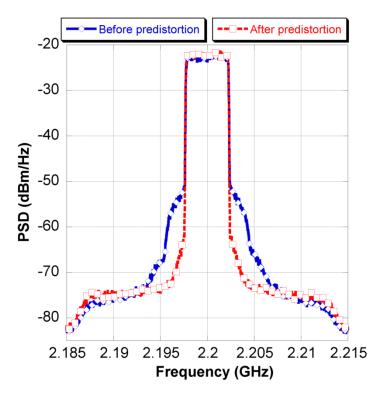

| Figure 4.15. LTE signal spectrum at the output of multi-branch topology.        | 83  |

| Figure 4.16. Spectrum of LTE signal with 5 MHZ bandwidth                        | 84  |

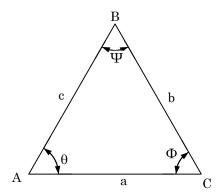

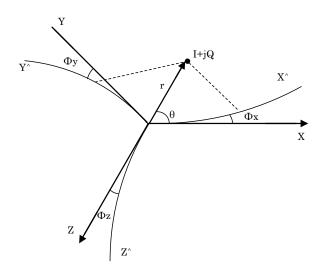

| Figure 5.1. Three-coordinate signal decomposition.                              | 87  |

| Figure 5.2. Law of sines representation.                                        | 88  |

| Figure 5.3. Three-way amplitude modulation-based transmitter architecture       | 89  |

| Figure 5.4. Phase response of VGA                                               | 91  |

| Figure 5.5. Signal decomposition based on new axes.                             | 91  |

| Figure 5.6. Predistortion and linearization.                                    | 95  |

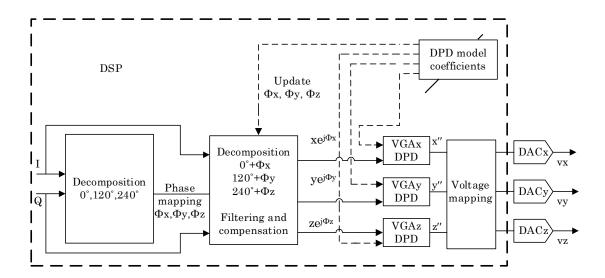

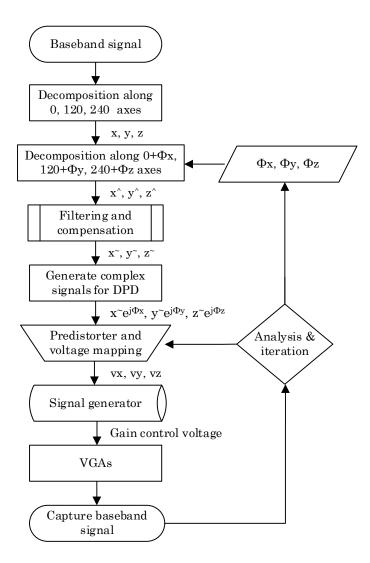

| Figure 5.7. Block schematic of the DSP.                                         | 96  |

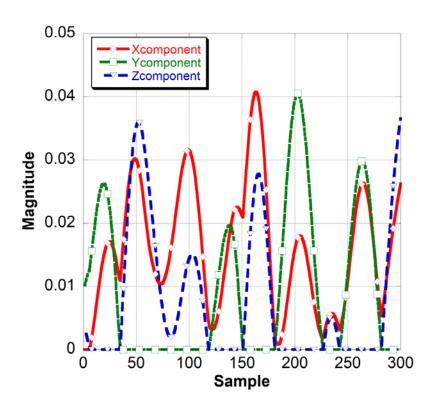

| Figure 5.8. Components obtained after signal decomposition                      | 97  |

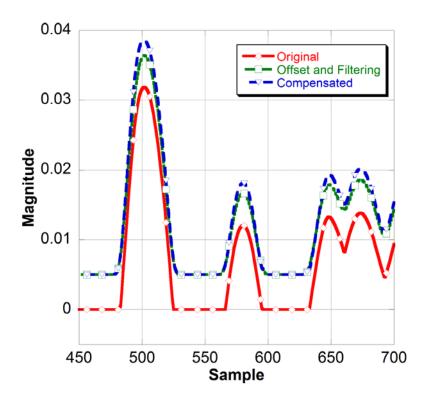

| Figure 5.9. Xcomponent after filtering and compensation.                        | 97  |

| Figure 5.10. Flow chart of DSP operation.                                       | 98  |

| Figure 5.11. Implementation of single path of transmitter.                      | 99  |

| Figure 5.12. LTE signal spectrum at the output of transmitter                   | 103 |

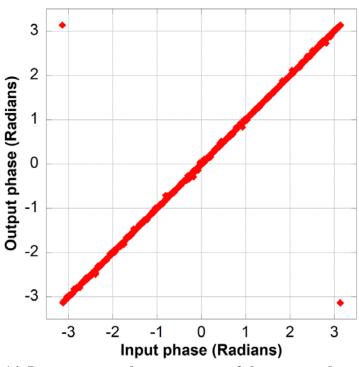

| Figure 5.13. Input-output envelope response of the proposed transmitter.        | 104 |

| Figure 5.14. Input-output phase response of the proposed transmitter            | 104 |

#### List of Symbols, Abbreviations and Nomenclature

**Symbol** Definition

3G Third Generation

3GPP 3<sup>rd</sup> Generation Partnership Project

4G Fourth Generation

ACLR Adjacent Channel-power Leakage Ratio

ACPR Adjacent Channel Power Ratio

ADC Analog to Digital Converter

ADS Advanced Design System

AGC Automatic Gain Control

AM-AM Amplitude Modulation to Amplitude Modulation

AM-PM Amplitude Modulation to Phase Modulation

BB Baseband

BER Bit Error Rate

BPF Band Pass Filter

BW Bandwidth

CMOS Complementary Metal Oxide Semiconductor

DAC Digital to Analog Converter

DC Direct Current

DPD Digital Predistortion

DSP Digital Signal Processing

EER Envelope Elimination Restoration

ESG Electronic Signal Generator

EVM Error vector Magnitude

FIR Finite Impulse Response

GSM Global System for Mobile

I Inphase

IC Integrated Circuit

I/Q Inphase/Quadrature

LO Local Oscillator

LUT Look Up Table

LTE Long Term Evolution

MXG Mixed signal generator

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

PAPR Peak to Average Power

PLL Phase Lock Loop

PM-AM Phase Modulation to Amplitude Modulation

PM-PM Phase Modulation to Phase Modulation

PWM Pulse Width Modulation

Q Quadrature

QAM Quadrature Amplitude Modulation

RF Radio Frequency

RFDAC Radio Frequency Digital-to-Analog Converters

SDR Software Defined Radio

Tx Transmitter

VSA Vector Signal Analyzer

VGA Variable Gain Amplifier

WCDMA Wireless Code Division Multiple Access

WLAN Wireless Local Area Network

#### Chapter One: Introduction

Wireless communication has become an inevitable part of our day to day lives. More than being a tool for conversation, it finds application in the field of engineering, medicine and military [1]. This tool which facilitates exchange of information plays a key role in the social and economic development of a country. The development in the integrated circuit industry has resulted in smart phones with better data and signal processing power. The reduced cost of production in semiconductor industry has also boosted the development of better communication devices. Smartphones that match the processing power of laptops and desktop machines have been developed in the recent years. To make use of the signal processing power of these phones, signal modulation schemes with higher data rate and efficiency are needed [2]. The demand for high speed communication systems has witnessed the development of different communication standards and protocols.

Different communication standards like Wireless Code Division Multiple Access (WCDMA) and Wireless Local Area Network (WLAN) should be supported by the devices. The communication industry has witnessed the evolution of 3GPP communication signals with higher data rate and complex modulation schemes [3]. Signal standards like Long Term Evolution (LTE), based on Orthogonal Frequency Division Multiplexing (OFDM) operates in different bandwidths and modulation schemes, and thus requires high performance transceiver systems [4]. Over the years, these communication standards have evolved to incorporate higher data rate, efficiency and better network security. LTE Advanced (LTE-A), evolved from LTE allows the operators to deploy bandwidths up to 100 MHz through carrier aggregation [5].

As these standards evolved, the development of radio hardware became inevitable. The evolution of different signals forces the upgrade or replacement of the existing radio hardware.

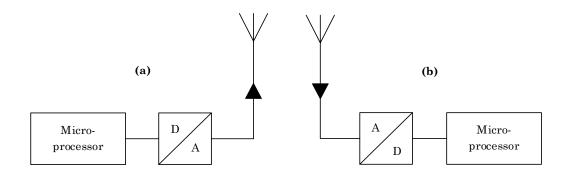

Figure 1.1. Ideal software defined radio: (a) transmitter, (b) receiver.

The new hardware should also have backward compatibility to support the devices which still work on older communication schemes.

The research community has always been trying to develop generic transceivers, which can cater to the needs of different standards. Thus, the evolution of modern communication signals has ignited the quest for multi-standard transceivers. There is immense research in developing transceivers which cater to the needs of these signals with complex modulation schemes. The aim has always been to move the digital domain of hardware as close as possible to the antenna to realize an ideal Software Defined Radio (SDR) [6].

An ideal SDR supports any kind of waveform by modifying the software or firmware, but keeping the hardware unchanged. In this definition, the term waveform refers to a signal which has a specific value for parameters like carrier frequency, modulation scheme etc. The ideal SDR as defined in [7] is shown in Fig. 1.1. The microprocessor performs the mapping of the user data to the desired waveform. The Digital to Analog Converter (DAC) directly converts the digital samples to RF signal, which will be transmitted by the antenna. In the receiver side, the signal captured by the antenna is sent to the Analog to Digital Converter (ADC). The digital samples obtained at the output of ADC will be processed by the microprocessor to get back the user data.

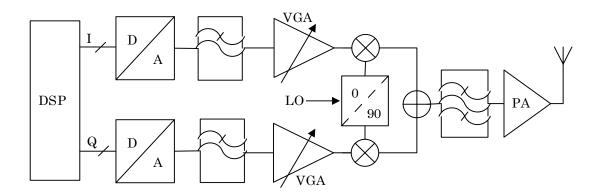

Figure 1.2. Conventional analog transmitter.

The progress towards such an ideal and elegant software radio has just started and there are several challenges in this journey. This thesis focusses on the transmitter side of the communication systems. In the progress towards an ideal transmitter, the parameters to be considered are integration, re-configurability and cost efficiency.

An ideal transmitter should not limit the bandwidth or the carrier frequency of the signal. Fig. 1.2 shows an implementation of a conventional analog transmitter. There are many off-chip components like power amplifiers and filters, which are band-limited. The DACs have to operate at very high sampling rates to have direct baseband to RF conversion architectures. Broadband power amplifiers are needed to meet a wide frequency range. There is multiple filtering involved to meet the spectrum masks and this limits the RF bandwidth of the transmitter chain. Rather than using multiple parallel chains of radios for different signals, radios that are multi-standard and reconfigurable are needed.

#### 1.1 Radio transmitter fundamentals

The transmitter and receiver are the key blocks of every radio. The transmitter performs the functions of digital modulation, frequency up-conversion and amplification of the signal before it is transmitted through the antenna.

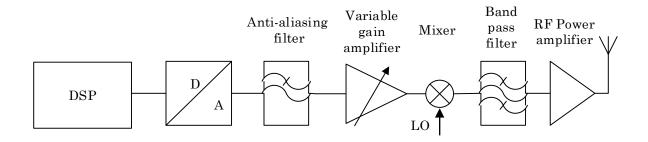

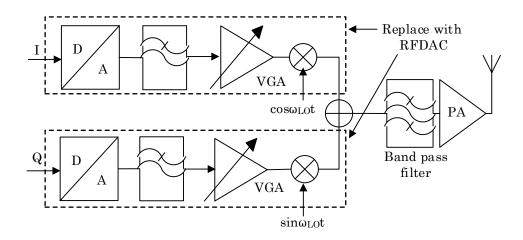

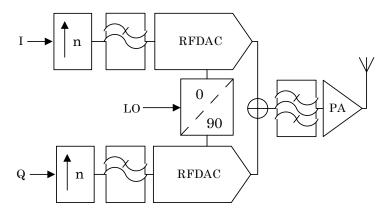

Figure 1.3. Conventional analog quadrature RF transmitter.

The commonly used transmitter architecture is the direct conversion transmitter topology [8] as shown in Fig. 1.3. The digital I and Q signals are given to the corresponding DACs. The DACs satisfy the Nyquist criterion, so as to move the DAC replicas away from the required band. These replicas are then removed by the reconstruction filters after the DAC. The gain of I and Q paths are adjusted using the VGAs and given to analog quadrature modulator. The Local Oscillator (LO) frequency is equal to the required RF frequency. This quadrature up-converter has two mixers which accept the LO with 0 and 90 degree phase shifts, and then multiplies them with I and Q signals respectively. Thus, the modulator translates the baseband IQ signal to RF. This signal is amplified by the RF power amplifier (PA) to the required power level, and then transmitted through the antenna. The filters are used to suppress the out-of-band emissions.

#### 1.2 Transmitter key parameters

#### 1.2.1 Linearity

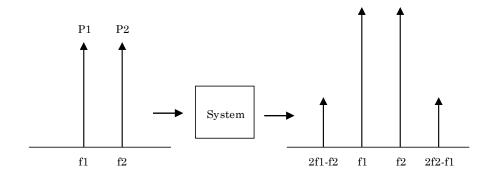

An important requirement of a transmitter is linearity. A transmitter is said to be highly linear if its output is directly proportional to the input signal. The transmitter should be highly linear to produce a signal of high quality and keep intermodulation distortion to a very low value. A signal applied to a nonlinear system results in harmonics, which is measured using a two tone test [9]. When a signal of two tones is fed into a nonlinear system, intermodulation products are obtained at different frequencies. The second order harmonics lie away from the required signal band and can be filtered out. The third order products are of critical importance as they fall close to the required fundamental tones as shown in Fig. 1.4.

Figure 1.4. Intermodulation: two-tone representation.

A high linearity of the transmitter results in intermodulation products of very low value as compared to the power of the fundamental tone and results in minimum in-band distortion to the signal. The out-of-band distortion results in spectrum regrowth and prevents the transmitters from adhering to the spectrum mask of the communication standard. The in-band distortion is quantified using a figure of merit called Error Vector Magnitude (EVM), while the out-of-band distortion is quantified using a figure of merit called Adjacent Channel Power Ratio (ACPR).

#### 1.2.2 Error vector magnitude

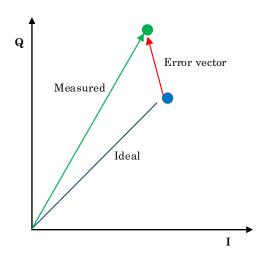

Error vector magnitude (EVM) is a measure of quality of modulation and the error performance in complex wireless systems. The performance of transmitters can be evaluated in terms of EVM. EVM measurements are also used as an alternative measurement for Bit-Error Rate (BER) measurements. Multi-symbol modulation schemes like Phase-Shift Keying (M-PSK) and Multi-level Quadrature Amplitude Modulation (M-QAM) use EVM as a performance metric. These modulation schemes are used in combination with Orthogonal Frequency Division Multiplexing (OFDM) modulation scheme in modern communication signals like Wireless Local Area Networks (WLANs) and Long-Term Evolution (LTE).

EVM is calculated as the vector difference at a given time between the ideal (transmitted) signal and the measured (received) signal. These measurements help in identifying the sources of signal degradation like IQ imbalance and nonlinearity.

Figure 1.5. EVM measurement in constellation.

EVM measurement is used to verify if the transmitter conforms to the 3GPP radio transmission standards. This standard has predefined EVM values for different modulation schemes and different signals like LTE and WLAN. Usually, it is stated as a percentage.

The EVM<sub>rms</sub> value, which is the RMS value of several error vectors averaged over the given time interval, is used in the performance evaluation of the transmitters for broadband modulated signals. As given in [10], EVM<sub>rms</sub> can be mathematically expressed as,

$$EVM_{RMS} = \sqrt{\frac{\frac{1}{N} \sum_{r=1}^{N} \left( \left| \mathbf{S}_{ideal,r} - \mathbf{S}_{meas,r} \right|^{2} \right)}{\frac{1}{N} \sum_{r=1}^{N} \left( \left| \mathbf{S}_{ideal,r} \right|^{2} \right)}} \times 100$$

(1.1)

where,  $S_{meas,r}$  is the normalized  $r^{th}$  symbol in a stream of measured symbols,  $S_{ideal,r}$  is the ideal normalized constellation point for the  $r^{th}$  symbol, and N is the number of unique symbols in the constellation.

#### 1.2.3 Adjacent channel power ratio

Adjacent channel power ratio (ACPR) is used to characterize spectral regrowth in nonlinear systems. In wireless communication, it is a measure that gives an idea about the signal distortion at the output of the power amplifier, the last stage of the transmitter. The nonlinearity in the device causes this spectral regrowth, which may cause interference in the adjacent channels.

ACPR can be defined as the ratio between the out-of-band power spectral density at the specified offset channel and the in-band power spectral density.

$$ACPR (dBc) = P_{offset} (dBm) - P_{inband} (dBm)$$

(1.2)

The offset frequencies and measurement bandwidths are defined for the standard that is used. For LTE signal waveform format, the term Adjacent Channel Leakage-power Ratio (ACLR) is used. In the case of LTE signal with a bandwidth of 1.4 MHz, the minimum ACLR requirement is 45 dBc [11]. LTE signal with a bandwidth of 1.4 MHz has a maximum occupied bandwidth of 1.08 MHz [12]. For ACLR measurements, an offset of 1.4 MHz is taken from the carrier and the

power is measured over a transmission bandwidth of 1.08 MHz around this offset. This power is compared with the channel power around the main carrier, measured over the same transmission bandwidth.

#### 1.3 Digital radio transmitters

Radio transmitters have evolved over a period of time to support broadband modulated signals. In this modern and highly competitive telecommunication market, these transmitter architectures should be cost effective along with optimum performance delivery. As mentioned in the introduction, the development in the CMOS industry has played a key role in reducing the production costs. However, to take advantage of this chip revolution, transmitters that are more integrable are to be developed. By avoiding bulky components, the cost and the size of these architectures can be reduced. As indicated in [13], CMOS process is suited for digital circuits as analog circuits cannot be scaled down continuously when a particular level of performance is targeted. The replacement of bulky analog components with their digital counterparts helps in reducing the power consumption and the chip area. This basic requirement has pushed the demand for more digital transmitter topologies.

There has also been a drastic demand for high speed DACs in transmitter circuits. The target was to increase the output frequency of these DACs so as to limit the number of mixing stages and analog blocks before the antenna [14]. However, these high speed conventional DACs have issues of sampling jitter and nonlinearity [15].

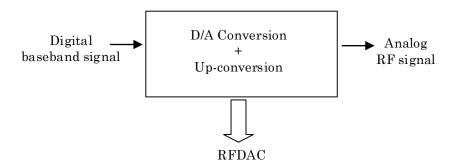

Several transmitter topologies have been proposed in literature to make the transmitters more digital and reconfigurable. A promising and a recently developed technique of making transmitters closer to the ideal SDR topology uses Radio Frequency Digital-to-Analog

Converters (RFDACs), which take the digital baseband signal as input and directly convert it to an analog RF signal at the output.

#### 1.3.1 RFDAC fundamentals

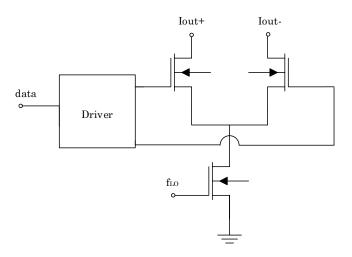

Figure 1.6. RFDAC representation.

In RFDACs, digital-to-analog conversion and frequency up-conversion mixing are combined into a single block. Hence, analog baseband processing can be avoided as the digital baseband signal is directly converted to analog RF. The baseband filters and the VGAs, as shown in Fig. 1.7 can be avoided by employing RFDACs [16].

Figure 1.7. Conventional transmitter with components replaceable with RFDAC [16].

Figure 1.8. Unit element of RFDAC proposed in [16].

The idea of RFDACs was put forward by Luschas et. al [16] and the team of Zhou and Yuan [17]. In these works, a modified topology of current-steering DACs was utilized to realize the architecture. The unit element of RFDAC proposed in [16] is shown in Fig. 1.8. A sine wave at the frequency of LO modulates the tail current source. The DAC output signal is converted to the frequency of LO signal through mixing operation. The unit elements of these RFDAC architectures had Gilbert cell [18] based mixer topology and the transistors were used as high speed switches.

RFDACs combine the mixer and DAC in a single current-steering stage. In the case of conventional direct conversion topologies, a trans-impedance stage converts the current output of current-steering DACs to a voltage for analog processing which includes filtering. After this analog processing, this voltage is converted back to current using a trans-conductance stage in front of the up-conversion mixer [13]. Conventional transmitter topologies which have several intermediate frequency stages, multiple voltage to current conversions happen, which affect the linearity of the system. In the case of RFDAC based architecture, the linearity of the output RF signal is affected only by the degradation in the Gilbert cell based mixers [17].

As the digital baseband signal is converted directly to analog RF, the DC offset in analog baseband signal is absent. Hence, carrier leakage due to this DC offset is avoided and the only leakage is due to the coupling of the LO signal to the output. As the trans-conductance stages are absent, the transistor mismatches are reduced, resulting in lower I and Q signal imbalances [19]. In normal IQ transmitters, reconstruction filters after the DACs are used to suppress the sampling replicas. The output of these filters is given as input to the mixers. However, in the case of RFDACs, as the DAC and mixer are combined together, this reconstruction filter after the DAC is absent. If these images are not suppressed, they get translated to RF and interfere with the required signal. In most of the previous works having RFDAC architecture based on mixer topology, different techniques are used to suppress these emissions. The challenges faced in combining the DAC and the mixer together into a single block are described in [13].

#### 1.3.2 Suppression of RFDAC emissions

Direct-digital modulators based on RFDACs employ different techniques to reduce the DAC emissions and distortion from the mixers. In [17] a direct-digital RF amplitude modulator, using a 10-bit linear interpolation current-steering DAC and a Gilbert cell based mixer was proposed to generate an amplitude modulated RF signal directly. Linear L-fold interpolation was employed in this architecture to suppress the DAC image components. The DACs generate linear and differential baseband current signals and they are sent to the mixer directly. As no low-pass filters are used, the trans-conductance stage used in conventional Gilbert cell based mixers is eliminated.

In [20], RFDAC based modulator was realized using delta-sigma modulator and a semi-digital FIR filter topology to suppress the noise and spurs. In this architecture, the digital IF signal is noise shaped using a band-pass sigma-delta modulator. This is followed by FIR filters, constructed using digital tapped delay lines and current sources. Inside the RFDAC there is an embedded current-mode mixer. The LO signals switch the current sources in mixer and upconvert the digital IF to analog RF. The up-converted currents are summed together to produce an analog RF output. According to the authors, the sources of non-idealities in this architecture are the filter coefficient errors, impedance matching and clock jitter. This architecture also needs FIR filters of higher length to reduce the out-of-band quantization noise for using this topology in wireless standards having stringent spectrum mask requirements.

A LC band-pass filter is used in [21] to suppress the images generated from the RFDAC architecture. Digital to RF modulator based on delta-sigma modulator is followed by a passive LC filter in this topology.

Fig. 1.9 shows a direct-digital modulator based on RFDACs proposed in [22]. Here, a 10-bit digital-to-RF converter is employed in both I and Q paths. In this architecture, the baseband signals are oversampled to move the replicas away from the signal band and are subjected to digital filtering to reduce the emissions and meet the spectrum mask. A LC tank circuit is used in this topology for proper output matching.

A more efficient direct-digital modulator based on RFDACs is proposed in [13]. In this architecture, baseband signals are oversampled and a delta-sigma modulator is used for noise shaping. The current outputs of weighted unit cells are summed together at the RF output. A LC tank circuit is employed to filter out the quantization noise and a Balun is used to ensure proper output matching.

Figure 1.9. RFDAC based direct-digital modulator proposed in [22].

In a recent work [23], all-digital IQ RFDAC prototype was experimentally demonstrated. Orthogonal summing of I and Q signals was employed for the realization of this promising architecture. This architecture uses a pair of digital to RF up-converters which comprise mixers and switch array banks. Differential I and Q clock signals are generated at the carrier frequency and then multiplied with the baseband I/Q signals through mixers and fed to transistor switch arrays. These outputs are then combined together using a power combiner. Transformer based power combiner is used here for RF signal addition as well as for impedance matching. As per the authors, the Balun power combining network and speed of the digital circuitry are the only two factors which limit the bandwidth of this architecture. Interpolation and FIR filtering is employed in this architecture to move the spectral images from the signal band and to suppress the emissions.

The architectures described in [13, 17, 20-23] are the popular direct-digital transmitter topologies based on RFDACs in literature. They help in avoiding the analog processing blocks as compared to traditional IQ modulators and increase the integration capability. These RFDAC architectures use a combination of current-steering DACs, mixer cells [13, 17, 22] and modified Gilbert cell topologies [23] for baseband signal up-conversion. These architectures use mixer topologies and face challenges with the nonlinearity and distortion from mixers. These high speed switching architectures based on IQ topology have challenges of intermodulation distortion and spurious emissions.

These transmitter architectures use different filtering techniques to reduce these emissions. The use of bulky RF filters reduces their ability of integration and reduces the RF bandwidth of these transmitter topologies.

These architectures also face challenges with power combining at the RF output, which limits the RF bandwidth of the architecture. The use of filters and power combiners also restrict the reconfigurability of these transmitter topologies.

#### 1.4 Polar transmitters

Figure 1.10. Conventional polar transmitter.

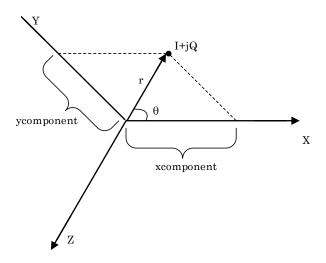

During the same tenure there was huge development in transmitter architectures based on polar topology. These, inspired from the popular EER technique [24], have also been referred to as RFDAC architectures and have evolved as promising candidates for direct-digital transmitters [25]. In polar modulators, baseband signal is modulated in the amplitude and phase domain rather than in the inphase and quadrature (IQ domain). The baseband IQ signal is decomposed into polar amplitude A (t) and a phase signal  $\Phi$  (t) according to,

$$A(t) = \sqrt{I(t)^{2} + Q(t)^{2}}$$

(1.3)

$$\phi(t) = \tan^{-1}\left(\frac{Q(t)}{I(t)}\right) \tag{1.4}$$

where, I and Q are the inphase and quadrature components of the complex IQ signal.

The phase signal  $\Phi$  (t) is converted to RF domain and then recombined with the envelope signal to get the complex RF signal. The phase modulated RF signal has a constant envelope. Hence, switch mode power amplifiers [26]; having higher efficiency can be used in these architectures. This in turn reduces the DC power consumption of transmitters [25].

Polar architectures offer better carrier suppression as compared to traditional IQ architectures. Polar transmitters have inherent challenges like bandwidth expansion due to nonlinear polar decomposition. The envelope and the phase signals have higher bandwidths as compared to the IQ signal. Polar architectures also demand accurate delay adjustment between the amplitude and phase paths. The envelope and phase signals should be recombined after proper delay adjustment to avoid any spectral emissions and to adhere to the spectrum mask of the wireless communication standard [27].

#### 1.4.1 Envelope and phase signal recombination

Polar transmitters use different techniques for envelope and phase path recombination. The most popular architecture is drain modulation or supply modulation [28, 29] as shown in Fig. 1.10. The phase modulated RF signal, with a constant envelope is fed to the input of a RF power amplifier (PA). The PA inserts the amplitude information by varying its supply voltage. This is achieved using DC-DC converter or switching regulator with good efficiency. As the input to the PA is a constant envelope signal, Switch mode PAs can be used in saturation and offer very high efficiency. The switch mode PAs are nonlinear and introduce distortion to the signal. Thus, these architectures require filtering and predistortion techniques [25]. These architectures require careful designing of supply modulators and have challenges of efficiency-bandwidth trade off. A detailed analysis of the distortion in supply modulation based polar architectures and modelling techniques used to compensate them are given in [30]. The issue of feed-through capacitance in these architectures has been addressed using envelope conditioning methods [31, 32].

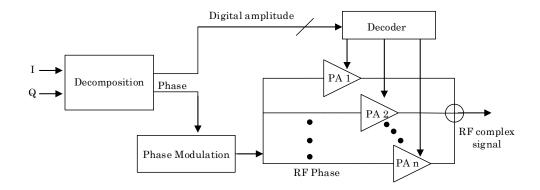

Figure 1.11. Polar transmitter using DPAs.

In [33-36] envelope and phase signal recombination was done using Digital Power Amplifiers (DPA). These architectures offer an alternative way of recombining envelope and phase components without using supply modulators. In these works, the phase modulated RF signal with constant envelope is given to a number of unit amplifiers which are switched according to the digital amplitude bits as shown in Fig. 1.11. The outputs of these unit amplifiers are then combined to get the complex RF signal. In these architectures, oversampling and linear interpolation are employed to reduce the spectral images. These architectures face challenges of power combining [33] and nonlinearity, and adopt digital predistortion techniques to compensate them [35].

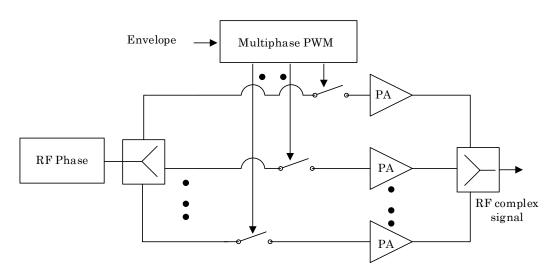

Polar transmitter architecture using pulse width modulation has been proposed in [37]. A multiphase technique using four parallel class C amplifiers driven by multiphase pulse-width modulated signals is used, instead of drain modulation. In this architecture, the use of multiphase technique increases the effective sampling frequency and helps in reducing out-of band emissions and relaxes the filtering requirements. In this work, the phase modulator was implemented using vector modulator. This work also analyses the challenges with power combining and its effect on the total efficiency of the transmitter.

A similar technique using interleaved pulse width modulation was used in [38]. The use of interleaving PWM technique helps in reducing the spurs and ease filtering requirements. This architecture uses high efficiency switch mode amplifiers for amplification. A commercially available SAW filter is used for band-pass filtering after the PA to restore the complex modulated signal.

Figure 1.12. Polar transmitter architecture proposed in [37].

Signal recombination has also been incorporated in polar architectures using variable gain amplifiers [39, 40]. The envelope component (AM) signal is generated digitally at the baseband and then fed into the gain control input of the VGA. The phase modulated RF signal with constant envelope is fed into the RF input of the VGA. The VGA will recreate the amplitude modulation by varying the gain according to the control signal. These architectures face challenges with the dynamic range and the update rate of the VGAs. VGA based architectures were used for standards like GSM/EDGE signals, but never used for OFDM signals like WCDMA and LTE.

Polar transmitter architecture using Class D<sup>-1</sup> PA array and transformer based power combining has been implemented in [41]. The baseband processing has been incorporated in FPGA. The output of individual PAs are given to the primary windings and the secondary windings are connected in series for power combining. Look up table (LUT) based predistortion is used here to compensate for the nonlinearity and oversampling is employed to reduce the out-of-band noise. The phase modulator section in this work is implemented using an external DAC and a modulator.

In one of the most recent works [42], a polar transmitter with an integrated phase path based on modified Gilbert cells was proposed. The amplitude path consists of unit amplifiers which are current-mode class D<sup>-1</sup> PAs. Transformer based power combining is employed and impedance is varied to achieve higher efficiency. The phase modulator is incorporated using an IQ phase interpolator. Inside the interpolator, differential-current DACs generate weighted IQ phases and LO signals, which are then summed like in quadrature mixers. FIR interpolation filters and high sampling rate is employed to suppress the spurs and noise generated. LUT based predistortion techniques have been used in this architecture to reduce the distortion.

The phase modulator section of all these architectures has been implemented using quadrature up-converters [28, 29, 41], external signal generators [36], vector modulators [37, 38] and Phase Lock Loop (PLL) circuits [39, 40].

The phase modulators based on quadrature up-converters have issues that are common to mixer based circuits. For the up-conversion of baseband phase component to RF domain, the use of mixers and quadrature up-converters could not be avoided. Hence, these architectures as well suffer from mixer spurs and distortion and require careful filtering design, which increases their foot-print and reduces their ability for integration.

PLL is an excellent phase modulation technique where phase modulation is directly applied to the synthesized RF carrier signal [25, 43]. It eliminates IQ up-converters and its associated spurious problems. The bandwidth constraints of PLL circuits have been solved using digital PLLs [43]. The phase signal obtained from IQ decomposition is differentiated to obtain the frequency deviations. This is fed to Digitally Controlled Oscillator (DCO) based modulator to generate phase modulated carrier signal. The tuning range of Voltage Controlled Oscillators (VCOs) and DCOs are critical in these techniques. PLL based architectures have challenges of phase noise, bandwidth and require pre-compensation techniques like digital filtering.

#### 1.5 Vector modulators

RF Vector Modulator enables independent control of amplitude and phase of narrowband RF signals [44].

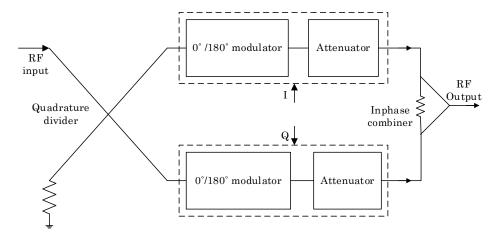

Figure 1.13. Block schematic of vector modulator.

The function of a vector modulator is to simultaneously control the phase and amplitude characteristics in the processing of a microwave signal [45]. The input signal is divided into two equal signals 90° apart using a 3 dB hybrid coupler as shown in Fig. 1.13. There are two variable attenuators capable of a 180° phase shift. The attenuation and the sign of each path are controlled by I and Q signals. The outputs of these two attenuators are combined using a Wilkinson power combiner. Each attenuator controls the magnitude with 180° phase shift resulting in four-quadrant operation. PIN diodes or GaAs MESFETs are used as attenuators that have an electrically controlled resistive component. PIN diode is operated as an attenuator by varying its junction resistance (Rj) with bias current.

The initial vector modulators used a combination of attenuator and phase shifters [46]. Latter modulators, which consist of a phase-splitting power-divider that creates either two or four channels, were proposed [47]. The individual channels are amplitude modulated and then power-combined in-phase. A quadrature 3 dB power divider is used to create the two orthogonal

channels. An individual bi-phase amplitude modulator is assigned to each channel. The output signals from these amplitude modulators are then combined using an inphase 3 dB power combiner. Vector modulators have been used for complex modulation schemes like QPSK and QAM [48].

Realization of analog vector modulator faces challenges of imbalances in I and Q signal paths, analog multiplier imperfections and isolation issues in input power splitting/output power combining networks. These frequency and signal dependent imperfections contribute to errors in the amplitude and phase of the signal in the modulation process. Feed-forward based calibration and predistortion techniques are used to compensate them [49]. The vector modulator also faces challenges with the phase error of the variable attenuators. This affects the phases of the signals at the output of the attenuators and causes distortion. The insertion losses from the attenuators and phase controllers affect the amplitude linearity of these modulators.

# 1.6 Summary of transmitter architectures

The transmitter architectures described in sections 1.3 and 1.4 are summarized in Table 1.1. The different techniques used for phase up-conversion in polar transmitters and their issues are summarized in Table 1.2.

**Table 1.1 Summary of architectures**

| RFDAC-BASED<br>MIXER<br>TOPOLOGY    | DRAIN<br>MODULATION                      | DPA                                      | VGA                                      |

|-------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| supports large<br>bandwidth         | spectrum growth-<br>limited bandwidth    | spectrum growth-<br>limited bandwidth    | spectrum growth-<br>limited bandwidth    |

| missing<br>reconstruction<br>filter | delay mismatch of amplitude & phase path | delay mismatch of amplitude & phase path | delay mismatch of amplitude & phase path |

| switching non linearity & losses    | linearity issues                         | linearity issues                         | linearity issues                         |

| clock speed issues<br>& jitter      | supply modulator<br>bandwidth            | power combining                          | update rate of VGA                       |

Table 1.2 Summary of phase modulation architectures

| QUADRATURE UP-<br>CONVERTER | PLL                    | GILBERT CELLS          |

|-----------------------------|------------------------|------------------------|

| noise & emissions           | noise                  | noise and emissions    |

| wide bandwidth              | low bandwidth          | wide bandwidth         |

| filtering requirements      | filtering requirements | filtering requirements |

# 1.7 Goals and objectives

The goal of this thesis work is the proposal and implementation of new transmitter architecture that is suitable for integration, and for multi-standard and multi-band reconfigurability.

More precisely, the objective is to avoid using mixers/quadrature modulators for frequency upconversion. As the mixers are avoided, the harmonic distortion and spurious emissions associated with them are nullified. This would result in eliminating the use of band limiting and bulky RF filters in the architecture, making the transmitter suitable for integration and reconfigurability.

The transmitter should be able to handle high data rate OFDM signals of current wireless communication standards such as LTE.

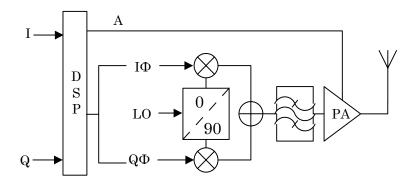

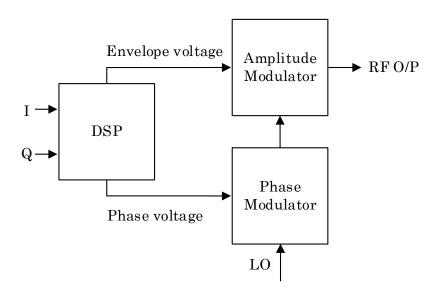

Figure 1.14. Block schematic of proposed architecture.

Fig. 1.14 shows a high level block diagram of the targeted architecture. This new architecture consists of an amplitude modulator and a phase modulator. The baseband amplitude and phase signals are mapped to voltages. These voltages drive the two modulators to produce a complex RF signal at the output. In this thesis work, the amplitude and phase modulators are implemented using a RF variable gain amplifier and an analog phase shifter respectively. While these components are not perfectly linear, reverse modeling will be sought and implemented in the digital signal processing block in order to compensate for any imperfection in the transmitter, resulting in acceptable signal quality along with the reconfigurability and suitability for integration assets.

#### 1.8 Thesis outline

This thesis is outlined as follows:

The fundamentals of radio transmitters for wireless communication is presented in chapter one. The key parameters and the performance metrics of a radio transmitter are discussed. The concept of direct-digital transmitters based on RFDACs and the different RFDAC architectures in literature are introduced. The advantages of RFDACs, the issue of RFDAC emissions and the techniques used to address them in literature are presented. This chapter also introduces the goal of this thesis work.

In chapter two, the fundamentals of a Variable Gain Amplifier (VGA) as amplitude modulator is presented. The modelling and linearization of gain response of VGA is discussed in detail. The implementation of VGA as an amplitude modulator is presented and the measurement results are discussed.

In chapter three, a new topology using an analog phase shifter as a phase modulator is presented. The challenges of using the phase shifter for phase up-conversion and the methods used to address them are presented here. The modelling and linearization of phase response of the phase shifter is discussed. Finally, the chapter is concluded with the implementation details and the measurement results.

In chapter four, the proposed architecture of the full transmitter is discussed. The transmitter translates the baseband signal to RF domain without using mixers. The responses of the key components, VGA and the phase shifter are evaluated. These responses have to be modelled for producing a high quality signal at the output of the transmitter. A new calibration technique is proposed to model the transmitter response. In this technique, a new reverse model is proposed to be used as a digital predistortion model. Finally, the implementation of the proposed

transmitter architecture is discussed. The chapter is concluded with the measurement results and the performance evaluation of the architecture.

In chapter five, another new RF transmitter architecture using only envelope modulators is proposed. The baseband complex signal is decomposed into components using three-coordinate system. These individual components are translated to RF using three VGA paths and then combined together to get back the complex signal at RF domain. A calibration technique is proposed to model the responses of the individual VGAs. Digital predistortion technique is employed to linearize the gain and phase response of the VGAs. The chapter is concluded with the implementation details and measurement results.

Finally, the thesis is concluded in chapter 6, with a brief summary of the major contributions achieved in this work. A proposal for future work direction is also presented.

#### 1.9 Conclusion

highlighted in this chapter.

This chapter gives an overview of the current scenario in wireless communication industry. The need for communication schemes with better efficiency and higher data rate was established. Furthermore, the ramification of the development of modern communication schemes on the radio hardware was discussed. The need for multi-standard and reconfigurable transmitters, which can cater to the demands of the 3GPP signals, was discussed. The need of a mixerless frequency up-converter that is more suitable for integration and reconfigurability is justified. Techniques highlighting state-of-the-art attempts to propose solutions for these needs, using RFDAC based architectures and polar architectures are reviewed. A comparison of these different solutions, their advantages and drawbacks are highlighted in this chapter. It was concluded that most of these architectures use mixers and quadrature up-converters for phase up-conversion and require filtering to suppress the emissions and to meet the spectrum mask.

This work proposes a new transmitter architecture using a VGA as an envelope modulator and a phase shifter as a phase modulator in order to perform a mixerless frequency up-conversion. This architecture rules out any filtering requirements. The goal and the outline of the thesis are also

2.1 Introduction

In chapter one, the concerns with the existing mixer-based IQ transmitter architecture and the polar RFDAC transmitter architecture was discussed. A new transmitter architecture was proposed using an amplitude modulator and a phase modulator. The amplitude modulator translates the baseband envelope information to RF domain. In this thesis work, amplitude modulator is realised using a RF variable gain amplifier (VGA). By varying the gain of the VGA according to the envelope signal, the envelope signal can be restored at the RF output of the VGA. Amplitude modulation using VGA has not been implemented in literature, for OFDM signals with complex modulation schemes and high Peak to Average Power Ratios (PAPR).

#### 2.2 VGA fundamentals

Variable gain amplifiers (VGAs) are amplifiers whose gain can be set to the required level using an external control voltage setting [50, 51]. Based on the method of application of control voltage, they are classified into analog and digital VGAs. The frequency range of operation of VGAs extends from dc to gigahertz frequencies. Analog VGAs have their gain (in dB) as a linear function of the gain control voltage and can be represented as

$$Gain(dB) = slope \times (vctrl - intercept)$$

(2.1)

where, slope is given as dB/volt, vctrl is the gain control voltage and intercept is the gain of the VGA when vctrl is 0V.

In the case of digital VGAs, a binary code or digital word applied to a digital port controls the gain. The word can be serial or parallel, and operates like a register. The binary steps will be weighted in dB.

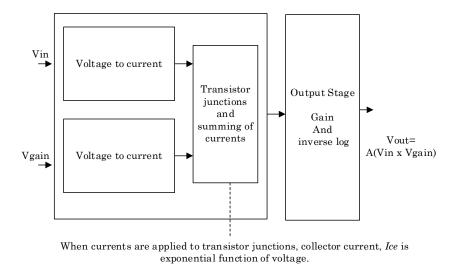

The internal architecture of VGAs can be classified mainly into two design approaches. In translinear approach, bipolar devices which operate on the principle of diode equation are used. They operate on the principle of exponential relationship between base voltage and junction current in bipolar devices [52]. The simplified block schematic of translinear VGA is shown in Fig. 2.1. VGAs based on this architecture have issues with noise and distortion and are used when reduced cost is the deciding factor [50].

Figure 2.1. Block schematic of translinear VGA.

In exponential type VGAs [53], a RxR ladder attenuator and an interpolator followed by a fixed gain amplifier is used as shown in Fig. 2.2. The attenuation of the variable attenuator is varied under the control of a voltage.

Figure 2.2. Block schematic of exponential type VGA.

The fixed gain amplifier has a negative feedback and has reduced distortion. The ac and transient responses are fixed as the gain is constant [54]. The attenuator consists of a R-2R ladder network (taps). The input of the amplifier can be connected to any of these taps, or interpolated between them to control the gain.

VGAs find their application in radio communication, to control the signals which exhibit wide dynamic range. This is done using Automatic Gain Control (AGC) circuits in the receiver chain. VGAs are also used to match an input signal level to the full scale input of the next device. They are also used to scale the voltage to compensate for the losses.

## 2.3 VGA as amplitude modulator

VGA can be used as an amplitude modulator where the gain control signal acts as the modulating signal. A continuous wave (CW) signal is given to the RF input port of the VGA. The modulating signal is mapped to a voltage, based on the slope and intercept of the VGA. The gain of the VGA is then varied according to this voltage and modulating signal is obtained at the

output of VGA, at RF domain. VGA as an amplitude modulator is shown in Fig. 2.3 and can be mathematically represented as,

$$V_{in}(t) = Re \left[ v_{in}(t) e^{j2\pi tt} \right]$$

(2.2)

$$V_{\text{out}}(t) = \text{Re}\left[\left\{m \times v_{\text{in}}(t)\right\} e^{j2\pi ft}\right]$$

(2.3)

$$m = v_c(t) \times \text{sensitivity of VGA}$$

(2.4)

$V_{in}$  (t) and  $V_{out}$  (t) are the complex RF signals at the input and output of the VGA respectively,  $v_c(t)$  is the gain control signal.

Figure 2.3. VGA as an amplitude modulator.

The envelope information is extracted from the complex IQ signal as

$$env = \sqrt{I^2 + Q^2} \tag{2.5}$$

In this thesis work, amplitude modulation is evaluated using VGA evaluation board from Analog Devices (ADL5330). The specifications of ADL5330 are given in Table 2.1. This VGA has a gain in dB response. Hence, a mapping is used to obtain the gain control voltage from the actual envelope signal and can be represented as

$$vctrl = 20 \times alog_{10}(env) + b$$

(2.6)

where, vctrl is the gain control voltage, env is the envelope signal obtained using (2.5) and the values of constants a and b are obtained from the DC gain response of the VGA.

**Table 2.1 Specifications of VGA ADL5330**

| SPECIFICATION                      | VALUE           |  |

|------------------------------------|-----------------|--|

| Gain range                         | 60 dB           |  |

| Control voltage range              | 0-1.4 V         |  |

| Linear-in-dB gain control function | 20 mv/dB        |  |

| Operating frequency                | 10 MHz to 3 GHz |  |

| Bandwidth on the gain control pin  | 3 MHz           |  |

# 2.4 VGA imperfections

In the case of an ideal VGA, the gain of the amplifier changes linearly with the control voltage. The phase of the RF signal, as it propagates through the VGA should remain constant. However, due to device error there can be nonlinearity in the gain and phase response.

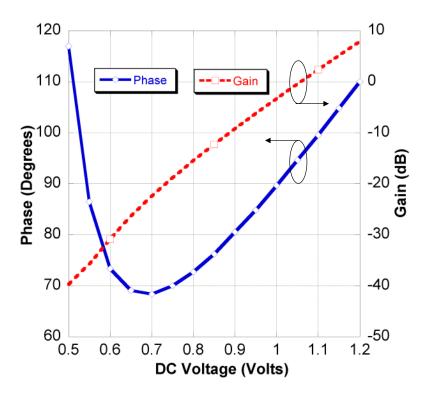

Figure 2.4. VGA gain and phase response.

The measured gain and phase response of the VGA using a DC voltage is shown in Fig. 2.4.

The DC response shows that the VGA has both Amplitude Modulation to Amplitude Modulation (AM-AM) and Amplitude Modulation to Phase Modulation (AM-PM) responses. VGA also exhibits memory effects like that of a RF power amplifier (PA) [55, 56]. The memory effect causes the output of the VGA to depend on the current input as well as the previous inputs. This nonlinearity and memory effects will affect the quality of amplitude modulated signal produced by the VGA. Thus, the VGA has to be calibrated and modelled to mitigate these imperfections.

#### 2.5 VGA calibration

The nonlinear gain response and the memory effects exhibited by the VGA are similar to that of a RF power amplifier. These effects can be modelled using a memory polynomial [57] and digital predistortion technique [58, 59] can be utilized to linearize the gain response of the VGA. The phase response of the VGA has to be corrected in an alternate chain where the phase can be controlled. The following section describes the modelling and linearization of the gain response of the VGA using memory polynomial.

#### 2.5.1 Memory polynomial calibration

A conventional memory polynomial with positive real coefficients is used to model the gain response of the VGA and can be represented as,

$$y(n) = \sum_{m=0}^{M} \sum_{k=1}^{K} a_{mk} x (n-m)^{k-1}$$

(2.7)

where,  $a_{mk}$  is the real predetermined calibration constant from a training signal. M is the memory depth and K is the nonlinearity order of the memory polynomial. x(n) and y(n) represent the

input and output envelope signals respectively. The memory polynomial models the nonlinearity and memory effects of the VGA in a single step.

A training sequence of 10,000 samples is given to the model and the coefficients are extracted using Least Squares (LS) technique [60]. The length of the training sequence is selected such that it is able to model the response of the VGA completely. Once the required training length is obtained, use of additional samples in the training sequence doesn't affect the modelling performance. Now, using the whole input sequence and using the coefficients extracted, the output is estimated. During modelling the values of nonlinearity order (K) and memory depth (M) are swept and for each combination of M and K, the Normalized Mean Square Error (NMSE) between the measured and estimated outputs is calculated to evaluate the accuracy of the model. The values of M and K corresponding to the lowest NMSE value are selected.

# Normalised Mean Square Error

The Normalised Mean Square Error is an estimator of the overall deviations between predicted and measured values. In other words, it gives a measure of difference between the value that is predicted by a model and the value that is actually measured.

The NMSE is defined as [61]:

NMSE (dB) =

$$10\log_{10} \left( \frac{1}{N} \sum_{n=1}^{N} \frac{\left| Y_{\text{meas}}(n) - Y_{\text{mod}}(n) \right|^{2}}{\left| Y_{\text{meas}}(n) \right|^{2}} \right)$$

(2.8)

where,  $Y_{meas}(n)$  and  $Y_{mod}(n)$  are the output waveforms measured and estimated from the model, respectively. N is the number of samples in the waveforms. The following section briefly describes the Least Square algorithm used to estimate the calibration coefficients from a training signal.

# 2.5.2 Least squares technique

Consider

$$B_k(n-m) = x(n-m)^{k-1}$$

(2.9)

The memory polynomial mentioned in (2.7) can be written in matrix format as,

$$\begin{pmatrix}

B_{1}(n) & ...B_{K}(n) & B_{1}(n-M) & ...B_{K}(n-M) \\

B_{1}(n+1)...B_{K}(n+1) & B_{1}(n+1-M) & ...B_{K}(n+1-M) \\

... & ... & ... \\

B_{1}(n+p-1)...B_{K}(n+p-1) & B_{1}(n+p-1-M) & ...B_{K}(n+p-1-M)

\end{pmatrix}

\begin{pmatrix}

a_{10} \\

a_{20} \\

a_{K0} \\

a_{1M} \\

... \\

a_{1M} \\

... \\

y(n+p-1)

\end{pmatrix}$$

(2.10)

Here x (n) refers to the input and y (n) refers to the output samples and p is the number of samples of the signal portion used for the model identification.

Then, the following matrix equation holds

$$\mathbf{B} \cdot \mathbf{a} = \mathbf{Y} \tag{2.11}$$

where, B is a  $[p \times (K \times M+1)]$  matrix and Y is  $(p \times 1)$  matrix

We have to find a  $[(K \times M+1) \times 1]$  to minimize the residual error.

The residue or error (r) in estimation of Y is defined as,

$$r=Y-B.a$$

(2.12)

The Least Squares approach seeks to find  $\hat{a}$  which minimizes the residue or error,  $\|r\|^2$ .

a is referred to as the Least Squares (approximate) solution of B. a = Y.

Assuming B is a full rank matrix, minimizing the norm of the residual squared gives;

$$r^{2} = r^{T}r = (Y - Ba)^{T}(Y - Ba)$$

(2.13)

$$r^{2} = Y^{T}Y - 2a^{T}B^{T}Y + a^{T}B^{T}Ba$$

(2.14)

Differentiating with respect to a and equating to zero gives;

$$\nabla_{a} \mathbf{r}^{2} = 2\mathbf{B}^{T} \mathbf{B} \mathbf{a} - 2\mathbf{B}^{T} \mathbf{Y} = 0 \tag{2.15}$$

This yields the normal equation,

$$\mathbf{B}^{\mathrm{T}}\mathbf{B}\mathbf{a} = \mathbf{B}^{\mathrm{T}}\mathbf{Y} \tag{2.16}$$

Assuming B<sup>T</sup>B is invertible,

$$\hat{\mathbf{a}} = \left(\mathbf{B}^{\mathsf{T}}\mathbf{B}\right)^{-1}\mathbf{B}^{\mathsf{T}}\mathbf{Y} \tag{2.17}$$

$B^{\dagger} = (B^{T}B)^{-1}B^{T}$  is called the pseudo-inverse of B.

This technique can be applied to the problem statement in (2.11) to obtain the vector of coefficients, a and can be represented as,

$$a = [a_{10} \quad a_{20} \quad \dots \quad a_{K0} \quad a_{1M} \quad \dots \quad a_{KM}]^T$$

(2.18)

From (2.17), a can be obtained as

$$a = B^{\dagger}Y \tag{2.19}$$

where,  $(B)^{\dagger}$  is the pseudo-inverse of B.

From the input signal and the coefficients extracted, the output of the VGA can be estimated as

$$Y_{est} = Ba \tag{2.20}$$

The error between measured and estimated data can be defined as

$$E = Y_{\text{meas}} - Y_{\text{est}} \tag{2.21}$$

The Least Squares estimate is constructed in such a way that  $||E||^2$  is minimized.

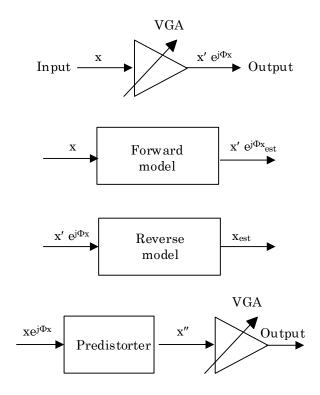

# 2.5.3 Digital predistortion technique

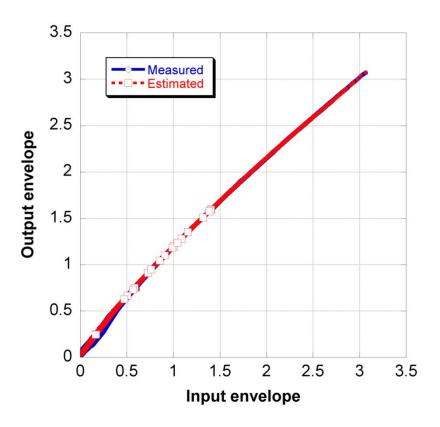

Using the Least Squares technique, the positive real calibration coefficients are obtained, which can be used to model the response of the VGA. Here, the input to the model is the actual envelope signal and output is the envelope of the complex signal captured at the output of VGA. The forward gain model of the VGA is shown in Fig. 2.5. In this figure, the blue line represents the measured output and the red line indicates the estimated output from Least Squares technique.

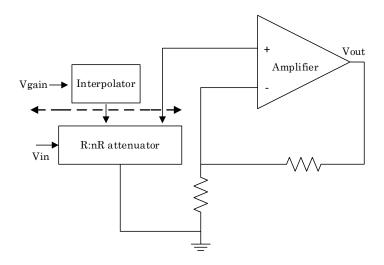

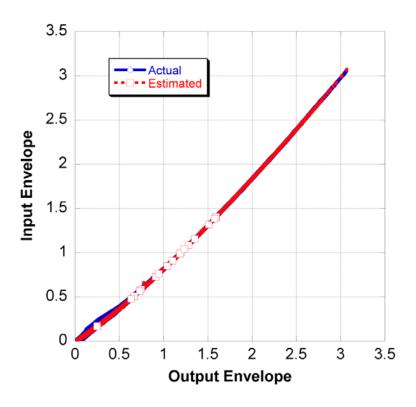

Now, using the same technique and swapping the input and output envelopes with each other, the reverse model of the VGA is obtained. Fig. 2.6 shows the reverse gain model of the VGA. Using the reverse model, the input is estimated from the output. This reverse modelling technique is used to extract the digital predistortion (DPD) coefficients as mentioned in [58].

Figure 2.5. VGA forward gain model.

Figure 2.6. VGA reverse gain model.

These coefficients are multiplied with the actual envelope signal to obtain the predistorted input signal. The predistorted signal when send through the actual VGA, linear response is obtained at the output of the VGA. Thus, the predistorter in cascade with the forward model of the VGA provides a linear system as shown in Fig. 2.7.

Figure 2.7. Predistortion and linearization.

# 2.6 Implementation

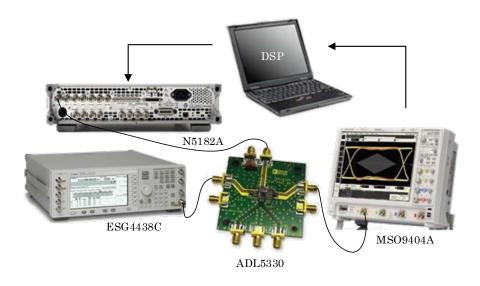

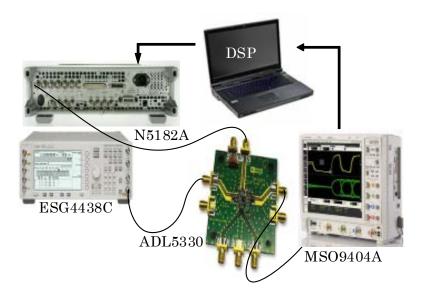

The amplitude modulator architecture is realised using the VGA evaluation board (ADL5330) as depicted in Fig. 2.8. The baseband IQ signal is generated using Agilent ADS software. From the complex IQ signal, the envelope information is extracted using (2.5) and mapped to voltage in MATLAB, using (2.6). The voltage thus obtained, is sent into the MXG/DAC (N5182A from Agilent Technologies). The Local Oscillator (LO) signal is generated using a signal generator (E4438C ESG from Agilent Technologies). The LO signal and baseband voltage generators are trigged in synchronization. The baseband output of the MXG gives the analog control voltage which is given to the gain control pin of the VGA. The LO signal is given to RF input port of the VGA. The RF signal at the output of VGA is captured using an oscilloscope (MSO9404 from Agilent Technologies) and digitized using VSA software (89600 series from Agilent Technologies).

Figure 2.8. Implementation of amplitude modulator using VGA.

The time alignment and further processing is carried out using MATLAB to retrieve the envelope information in the captured signal. The original envelope  $(A_{in})$  and the captured

envelope ( $A_{out}$ ) are multiplied with the phase component of the original complex signal ( $\varphi_{in}$ ) to obtain the input complex signal ( $A_{in}e^{j\varphi^{in}}$ ) and output complex signal ( $A_{out}e^{j\varphi^{in}}$ ), respectively. The NMSE of the output IQ signal as compared to the original IQ signal is used to evaluate the performance of the VGA. Hence, in this evaluation we have assumed that the phase error of the VGA is zero and that the phase components of the input and output complex signals are identical.

#### 2.7 Measurement results

To validate the proposed calibration technique and to evaluate the performance of the VGA, a LTE signal is generated using ADS software and sent to the setup as described above. The LTE signal is oversampled by 16 and baseband signal has 100,000 samples, sampled at a rate of 30.72 Msamples/s. The LO signal is at 2.2 GHz and has power level of -10 dBm. The results are summarized in Table 2.2.

Table 2.2 Summary of performance of the VGA for LTE signal

| SPECIFICATION                    | VALUE        |

|----------------------------------|--------------|

| Signal bandwidth (MHz)           | 1.4          |

| NMSE before DPD (dB)             | -24.51       |

| NMSE after DPD (dB)              | -50.04       |

| Nonlinearity order, Memory depth | K = 5; M = 2 |

| ACLR before DPD (dBc)            | 33.97        |

| ACLR after DPD (dBc)             | 57.62        |

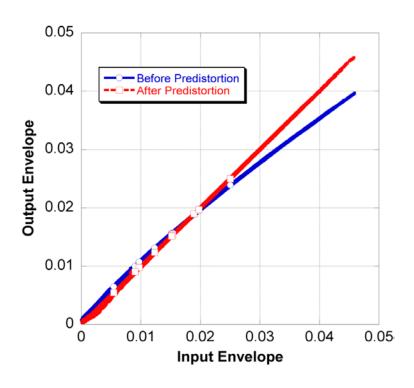

Figure 2.9. Input-output envelope response of the VGA.

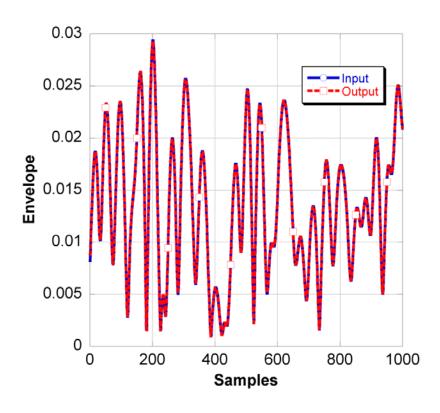

Figure 2.10. Time domain envelope response of the VGA.

The NMSE value, calculated using the amplitude of the signal only while ignoring the phase distortion, has improved by more than 25 dB after using digital predistortion technique. Fig. 2.9 shows the input-output envelope response of the VGA before and after adopting digital predistortion. The linearization technique works well and the VGA accurately reproduces the input envelope at its RF output port.

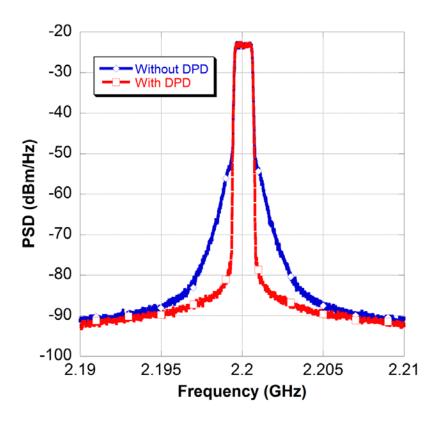

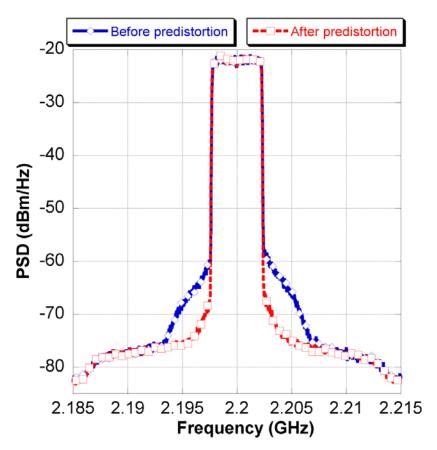

Figure 2.11. VGA spectral response.

Fig. 2.10 shows the time domain representation of the envelope at the output of the VGA and the spectral responses are shown in Fig. 2.11. From the spectral response, it is evident that the signal distortion introduced by the nonlinearity of VGA has been reduced to a great extent using digital predistortion technique. The ACLR has improved by 24 dB after adopting digital predistortion technique.

#### 2.8 Conclusion

In this chapter, the implementation of an amplitude modulator using a VGA was discussed. The theory and equations describing the VGA operation as an envelope modulator were outlined. The limitation of the VGA in terms of its nonlinear gain and phase response was discussed. Consequently, a calibration technique to mitigate the nonlinear gain response was presented and validated through measurement. A memory polynomial was used to model the VGA gain response. The performance of the VGA was evaluated using a LTE signal of 1.4 MHz bandwidth. The NMSE on the complex LTE signal at the output of variable gain amplifier (VGA) was improved from -24 dB to -50 dB after adopting digital predistortion technique. The results obtained, proved that the VGA can be used to implement a very linear amplitude modulator of the proposed transmitter architecture.

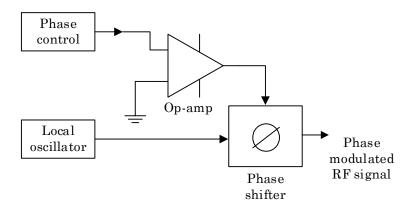

3.1 Introduction

This chapter deals with the implementation of the phase modulator architecture using an analog phase shifter. The phase modulator translates the baseband phase signal to RF domain without using a mixer or PLL circuit. The control voltage of the phase shifter is varied according to the baseband phase signal and a phase modulated RF signal is obtained at the output. Phase shifters have been used in literature to control the discrete phases and for phase error compensation [62, 63]. However, the implementation of phase modulator section of a RF transmitter using phase shifters is not mentioned in literature. The implementation of modulator using phase shifters faces different challenges, mainly the phase discontinuity, which results in distortion and ringing. The transition nature of the phase signal prevents the use of phase shifters for phase upconversion and forces the use of traditional quadrature modulators. Once this issue is resolved, mixerless topologies would become possible. Different techniques to cope with these challenges

have been proposed and will be validated in this chapter.

#### 3.2 Phase shifter fundamentals

Phase shifters are devices capable of shifting the phase of an electromagnetic wave at a given frequency while propagating through a transmission line [64]. The major parameters which need to be considered for a RF phase shifter are:

- Switching speed

- Frequency range

- Bandwidth

- Phase range

- Insertion loss

Commercially available phase shifters operate over a wide frequency range from few megahertz to gigahertz frequencies. Phase shifters are used in phase discriminators [65], linearization of power amplifiers [66] and phase array antennas [67]. They can be classified as

### 1. Microwave phase shifters

Microwave phase shifters give a predefined phase shift to a high frequency signal. They are realised using combination of transmission lines and switch circuits.

## 2. Switched-line phase shifters

In this type of phase shifter, a time delay difference between two direct paths is used to provide desired phase shift [68]. The switching elements in digital phase shifters are: mechanical switches (or relays), PIN diodes, Field Effect Transistors (FET), or micro-electromechanical systems (MEMS). PIN diodes are commonly used in these phase shifters due their high speed switching and low loss [69]. Switched-line phase shifters generally, are used for 180° and 90° phase shifts.

## 3. Digital multi-bit phase shifters

These phase shifters provide discrete set of phase states that are controlled by "phase bits". They offer a phase shift range up to 360°. A number of binary weighted phase shifting "bits" are

cascaded to realize the desired phase shift range. A number of fixed time delays are combined to produce successive increments of delay in response to binary control signals.

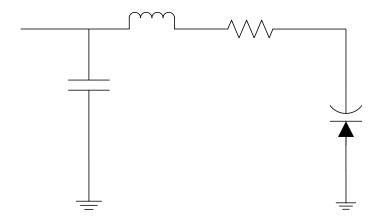

## 4. Analog phase shifters